THIS DOCUMENT AND ITS CONTENTS ARE THE PROPERTY OF DAVE NUTTING ASSOCIATES, INCORPORATED AND BALLY MANUFACTURING CORPORATION. THE INFORMATION CONTAINED HEREIN IS BOTH PROPRIETARY AND CONFIDENTIAL.

NO PART OF THIS DOCUMENT MAY BE REPRODUCED, STORED IN A RETRIEVAL SYSTEM, OR TRANSMITTED IN ANY FORM OR BY ANY MEANS ELECTRONIC, MECHANICAL, CHEMICAL, PHOTOGRAPHICAL, RECORDING, PHOTOCOPYING OR OTHERWISE.

DAVE NUTTING ASSOCIATES, INCORPORATED ASSUMES NO RESPONSIBILITY FOR THE USE OF ANY CIRCUITRY OTHER THAN CIRCUITRY EMBODIED IN A DAVE NUTTING ASSOCIATES, INCORPORATED DESIGNED PRODUCT.

THIS DOCUMENT MUST BE RETURNED TO DAVE NUTTING ASSOCIATES, INCORPORATED BY REGISTERED MAIL WITHIN 5 DAYS UPON WRITTEN DEMAND.

<sup>(</sup>C)1978 DAVE NUTTING ASSOCIATES, INCORPORATED

<sup>(</sup>C)1978 BALLY MANUFACTURING CORPORATION

# TABLE OF CONTENTS - SOFTWARE

| 1  |        | Home Video Game System               |

|----|--------|--------------------------------------|

| 2  |        | User Program Interface               |

| 5  |        | System Routine Conventions           |

| 7  |        | Inline Argument Mask Table Entry     |

| 8  | INTPC  | Begin Interpreting                   |

| 9  | XINTC  | Exit Interpreter                     |

| 1Ø | RCALL  | Call Assembly Language Subroutine    |

| 11 | MCALL  | Call Interpreter Subroutine          |

| 12 | MJUMP  | Interpreter Jump                     |

| 13 | MRET   | Return From Interpretive Subroutines |

| 14 |        | Screen Handler                       |

| 15 | SETOUT | Set Display Ports                    |

| 16 | FILL   | Fill A Contiguous Area With Constant |

| 17 | RECTAN | Paint A Rectangle                    |

| 18 |        | Screen Write Routines                |

| 19 |        | Standard Calling Sequence            |

| 2Ø |        | Pattern Representation               |

| 21 | VWRITR | Write Relative From Vector           |

| 22 | WRITR  | Write Relative                       |

| 23 | WRITP  | Write With Pattern Size Scare Up     |

| 24 | WRIT   | Write Pattern                        |

| 25 | WRITA  | Write Absolute                       |

| 26 | SAVE   | Save Area                            |

| 27 | RESTOR | Restore Area                         |

| 28 | VBLANK | Blank From Vector                    |

| 29 | BLANK  | Blank Area                           |

| 3Ø | SCROLL | Scroll Window                        |

| 31 |        | Screen Alphanumeric Display Routines         |

|----|--------|----------------------------------------------|

| 34 | DISNUM | Display BCD Number                           |

| 35 | DISTIM | Display Time                                 |

| 36 | CHRDIS | Display Character                            |

| 37 | STRDIS | Display String                               |

| 38 |        | STRDIS Interpretation of Codes 64H to 7FH    |

| 39 |        | Screen Vectoring - Vectoring Routines        |

| 42 | VECT   | Vector Object In Two Dimensions              |

| 43 | VECTC  | Vector A Co-ordinate                         |

| 44 | RELABS | Convert Relative Co-ordinates                |

| 45 | RELAB1 | Convert Relative Address To Absolute         |

| 46 | COLSET | Set Color Registers                          |

| 47 | INCSCR | Increment Score And Compare To End Score     |

| 48 | PAWS   | Pause                                        |

| 49 | KCTASC | Key Code to ASCII                            |

| 5Ø | SENTRY | Sense Transition                             |

| 53 | DOIT   | Respond To Input Transition                  |

| 54 | PIZBRK | Coffee Break, Black Out Screen, Wait For Key |

| 55 |        | Example                                      |

| 56 |        | Interrupt - Music Processor                  |

| 57 |        | MUZCPU Instruction Set                       |

| 58 |        | Music Score Example                          |

| 59 | BMUSIC | Begin Playing Music                          |

| 6Ø | EMUSIC | Stop Music                                   |

| 61 | ACTINT | Active Interrupts                            |

| 62 | DECCTS | Decrement Counter/Timers                     |

| 63 | CTIMER |                                              |

| 64         | STIMER | Decrement Timers                     |

|------------|--------|--------------------------------------|

| 65         | MOVE   | Move Bytes                           |

| 66         | INDEXN | Index Nibble                         |

| 67         | STOREN | Store Nibble                         |

| 68         | INDEXW | Index Word                           |

| 69         | INDEXB | Index Byte                           |

| 7Ø         | SETB   | Store Byte                           |

| 71         | SETW   | Store Word                           |

| 72         |        | Cassette Conventions                 |

| 75         | GETPAR | Get Game Parameter                   |

| 76         | MENU   | Display Menu And Branch On Selection |

| 77         | GETNUM | Get Number                           |

| 79         | MSKTD  | Joystick Mask To Deltas              |

| 8 <b>ø</b> | RANGED | Ranged Random Number                 |

|            |        |                                      |

# TABLE OF CONTENTS - HARDWARE

| 81         | Introduction           |

|------------|------------------------|

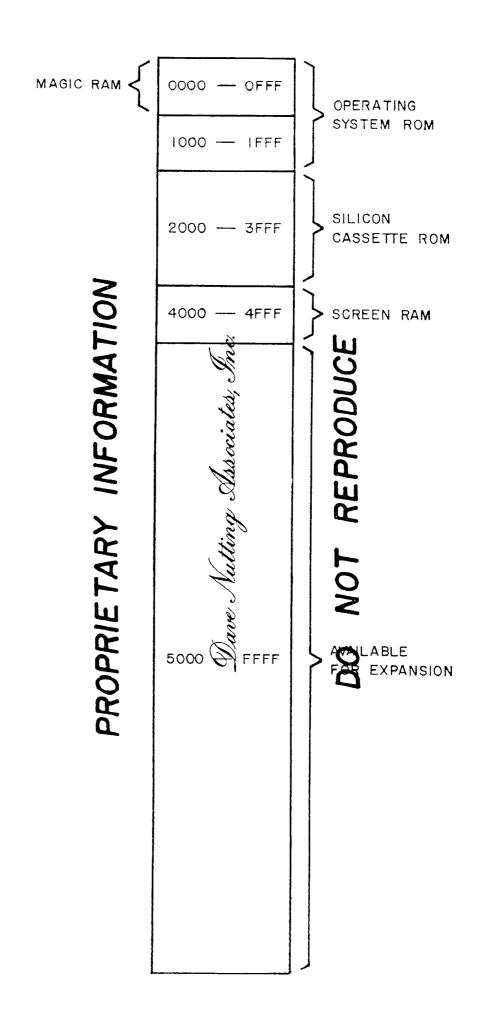

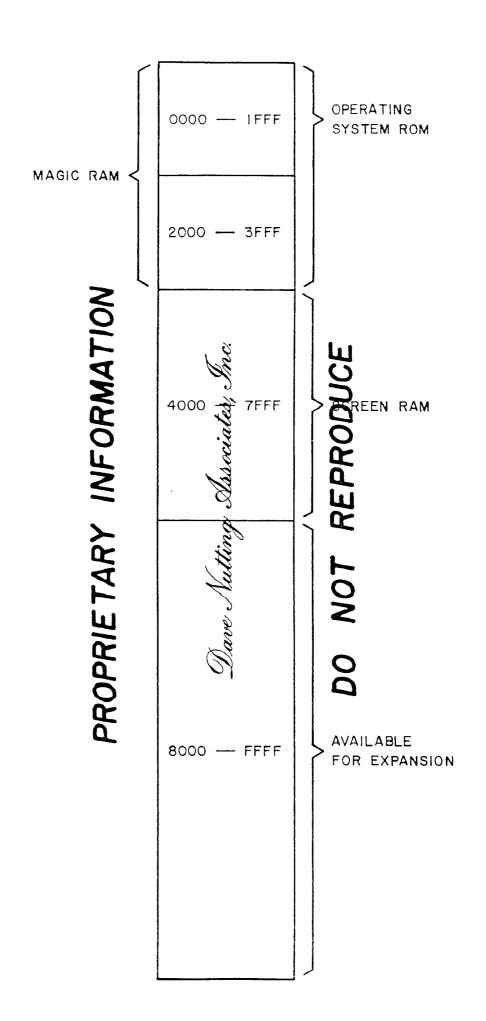

| 82         | Memory Map             |

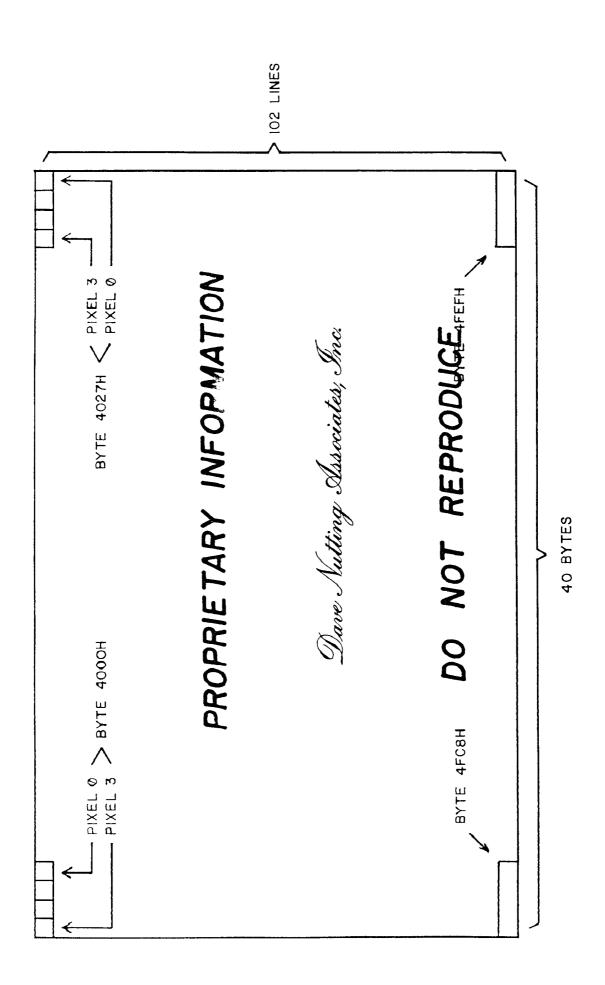

| 85         | Screen Map             |

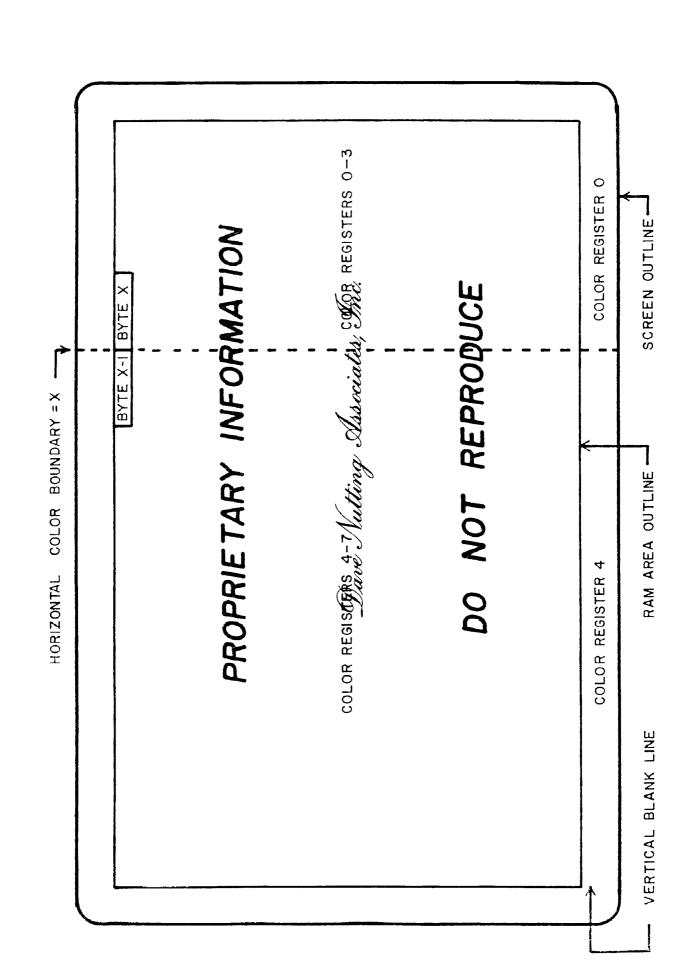

| 88         | Color Mapping          |

| 89         | Background Color       |

| 9 <b>ø</b> | Vertical Blank         |

| 92         | Interrupt Feedback     |

| 92         | Interrupt Control Bits |

| 93         | Screen Interrupt       |

| 93         | Light Pen Interrupt    |

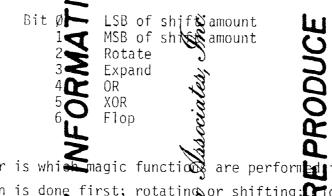

| 94         | Magic Register         |

| 95         | Expand                 |

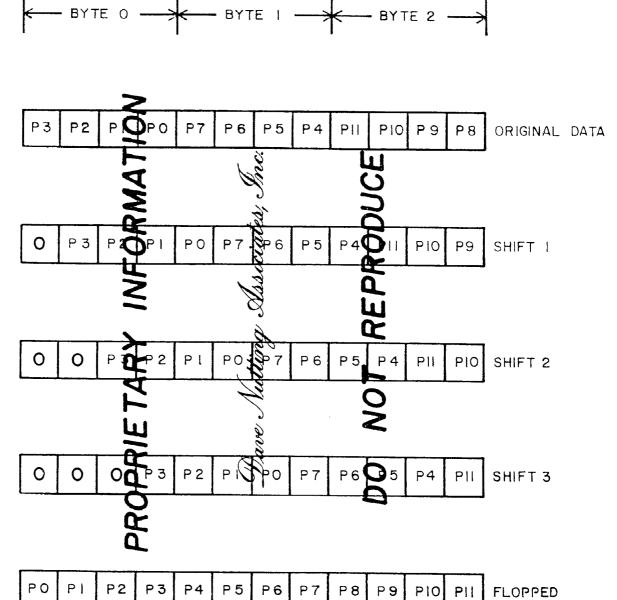

| 96         | Shifter                |

| 96         | Flopper                |

| 98         | Rotator                |

| 100        | OR And XOR             |

| 100        | Intercept              |

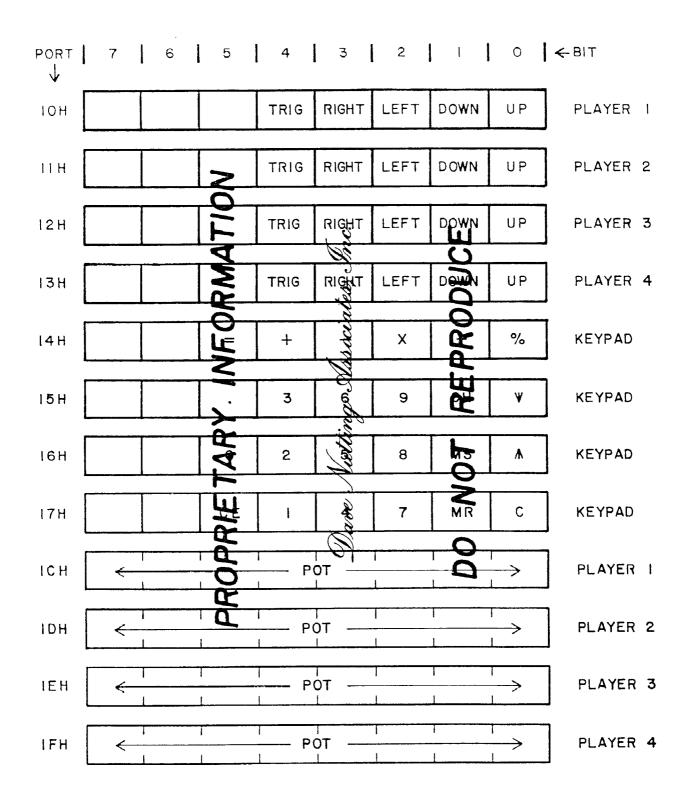

| 1Ø1        | Player Input           |

| 1Ø3        | Master Oscillator      |

| 1Ø4        | Tones                  |

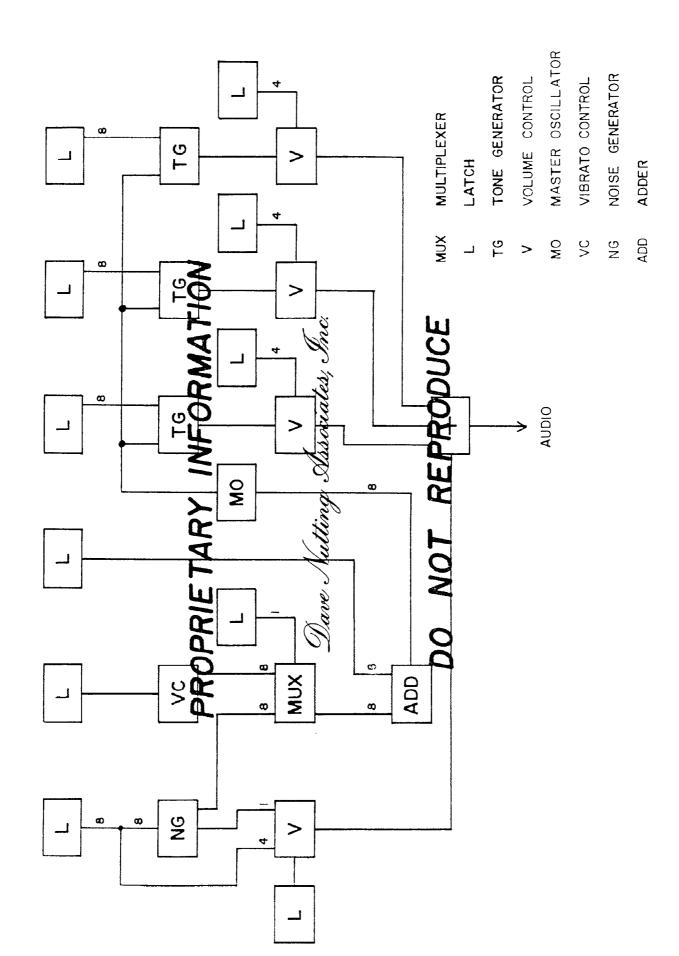

| 1ø4        | Sound Block Transfer   |

| 1Ø6        | Output Ports           |

| 1Ø7        | Input Ports            |

|            |                        |

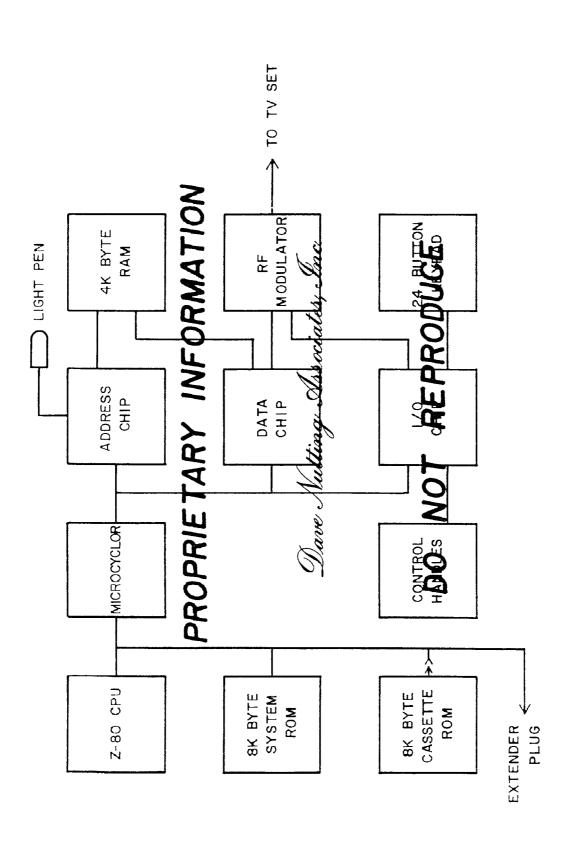

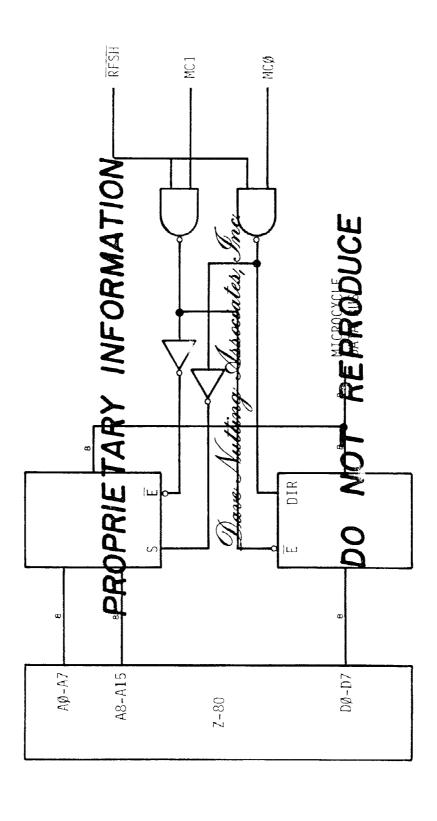

| 1Ø9 | Microcycler                                             |

|-----|---------------------------------------------------------|

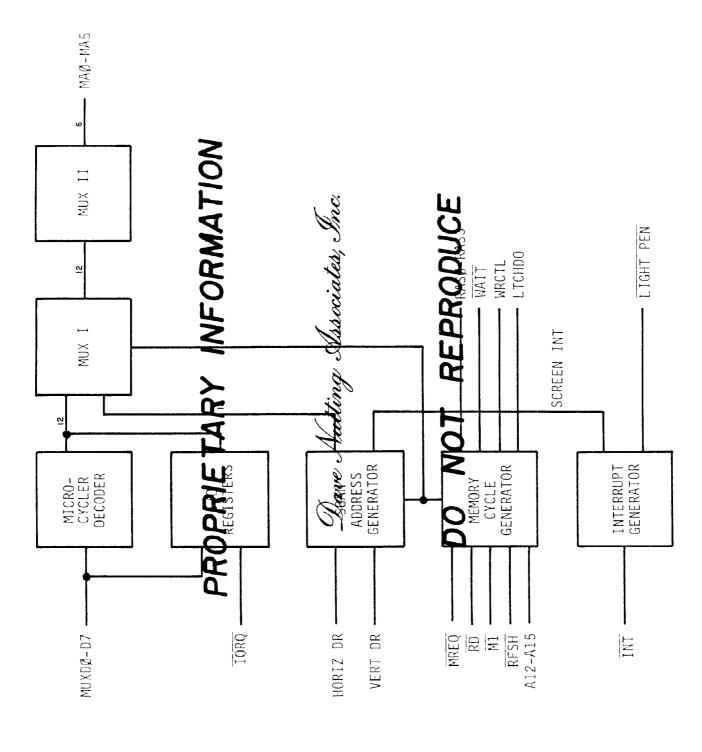

| 111 | Address Chip Description                                |

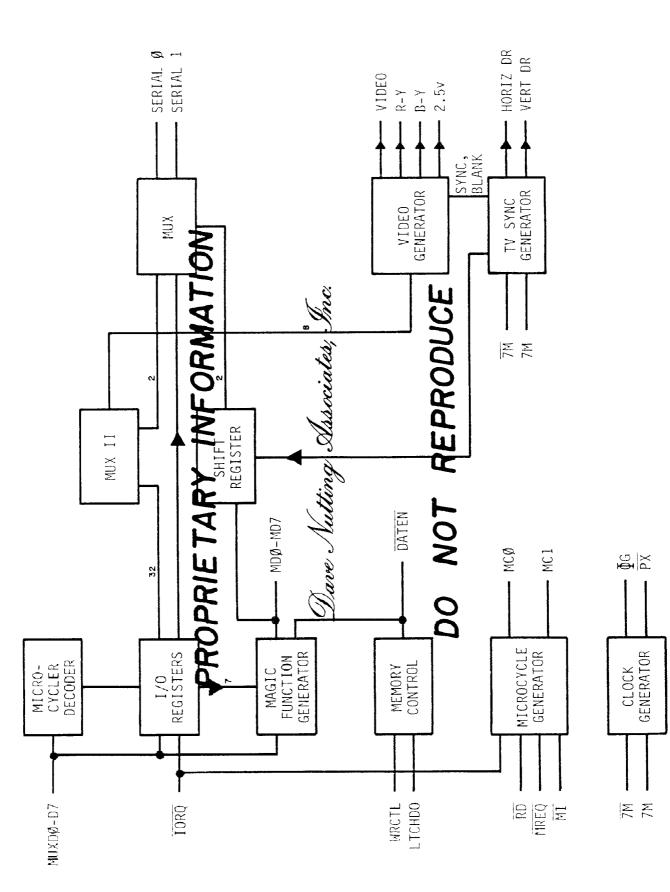

| 114 | Data Chip Description                                   |

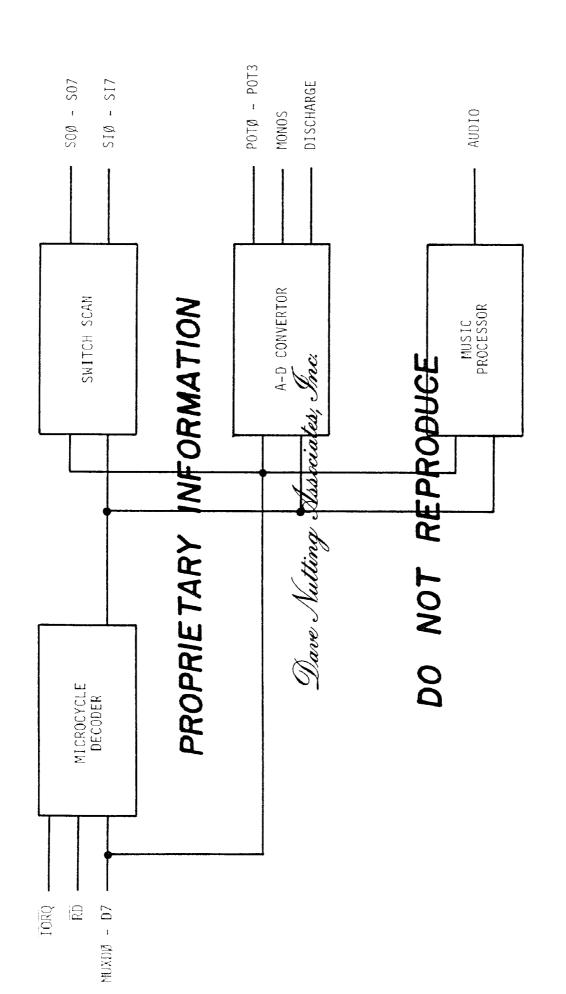

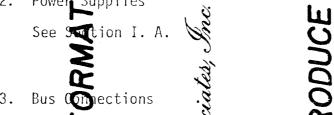

| 117 | I/O Chip Description                                    |

| 119 | Music Processor                                         |

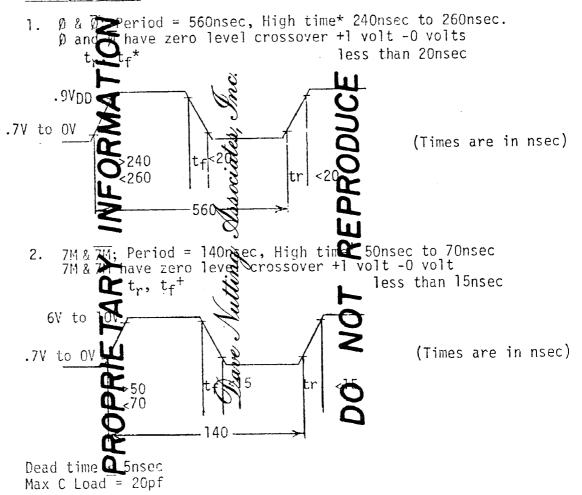

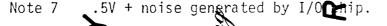

| 123 | Custom Chip Timing                                      |

| 131 | Video Timing                                            |

| 135 | Electrical Specifications for<br>Midway Custom Circuits |

# LIST OF ILLUSTRATIONS

| 6    | Context Block Format                   |

|------|----------------------------------------|

| 2Ø   | Pattern Representation                 |

| 32   | Option Byte                            |

| 33   | Alternate Font Descriptor              |

| 4Ø   | Vector Block                           |

| 41   | Vector Status Detail                   |

| 41   | Checks Mask Detail                     |

| 44   | Normal and Flopped Co-ordinate Systems |

| 51   | Keypad Mask Configuration              |

| 56   | Voices Status Register                 |

| 66   | INDEXN                                 |

| 68   | INDEXW                                 |

| 74   | Cassette Map                           |

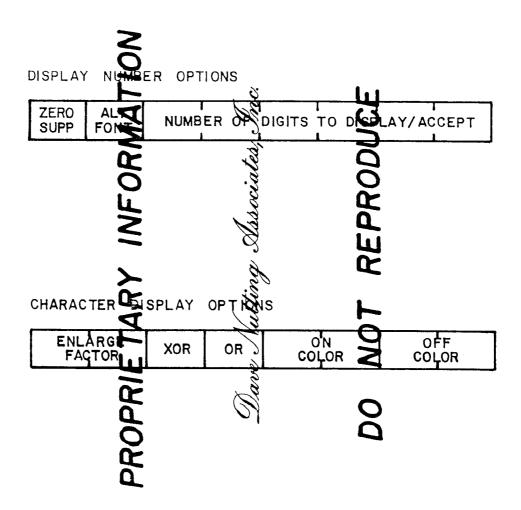

| 78   | Display Number Options                 |

| 78   | Character Display Options              |

|      |                                        |

|      | •                                      |

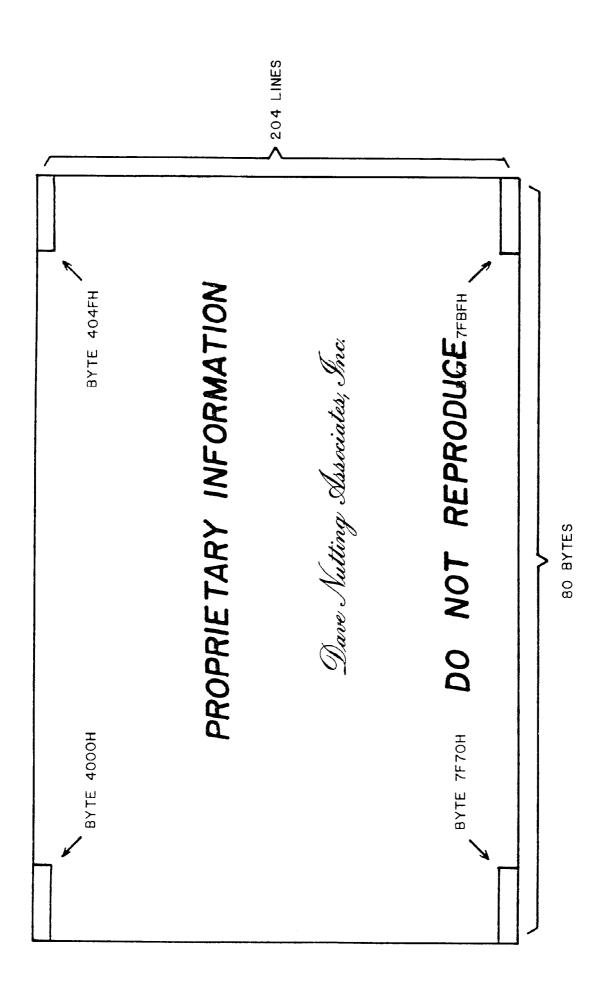

| 83   | Memory Map Low Resolution              |

| 84   | Memory Map High Resolution             |

| 86   | Screen Map Low Resolution              |

| 87   | Screen Map High Resolution             |

| 91   | Color Register Map                     |

| 97   | Shifter - Flopper                      |

| 99   | Rotator                                |

| 10/2 | Player Input                           |

| 1Ø5  | Audio Generator Block Diagram          |

| 1Ø6  | Output Ports                           |

|      |                                        |

| 1Ø7 | Input Ports                                    |

|-----|------------------------------------------------|

| 1Ø8 | System Block Diagram                           |

| 11Ø | Microcycler Block Diagram                      |

| 113 | Address Chip Block Diagram                     |

| 116 | Data Chip Block Diagram                        |

| 118 | I/O Chip Block Diagram                         |

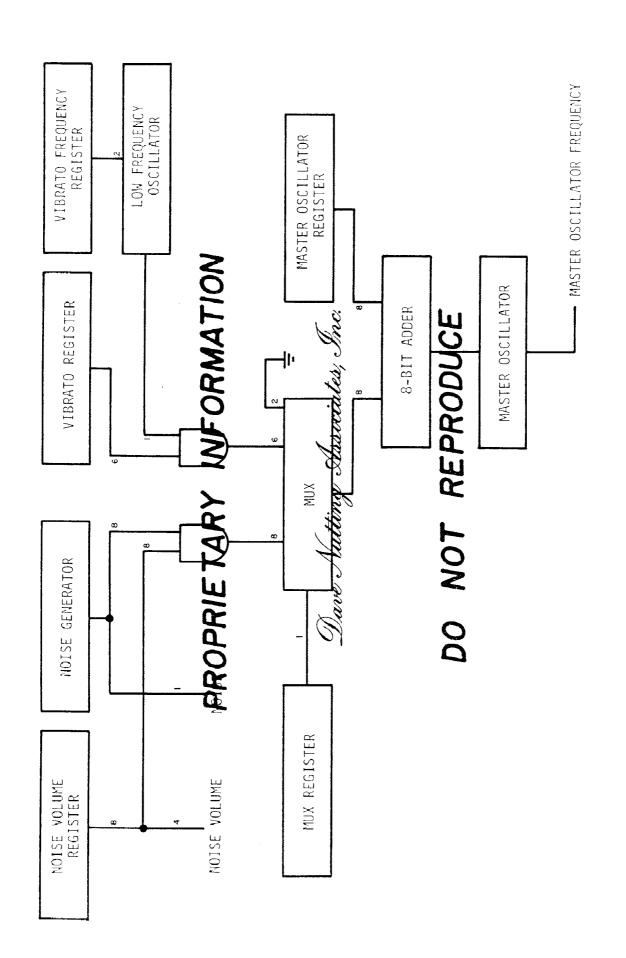

| 121 | Master Oscillator                              |

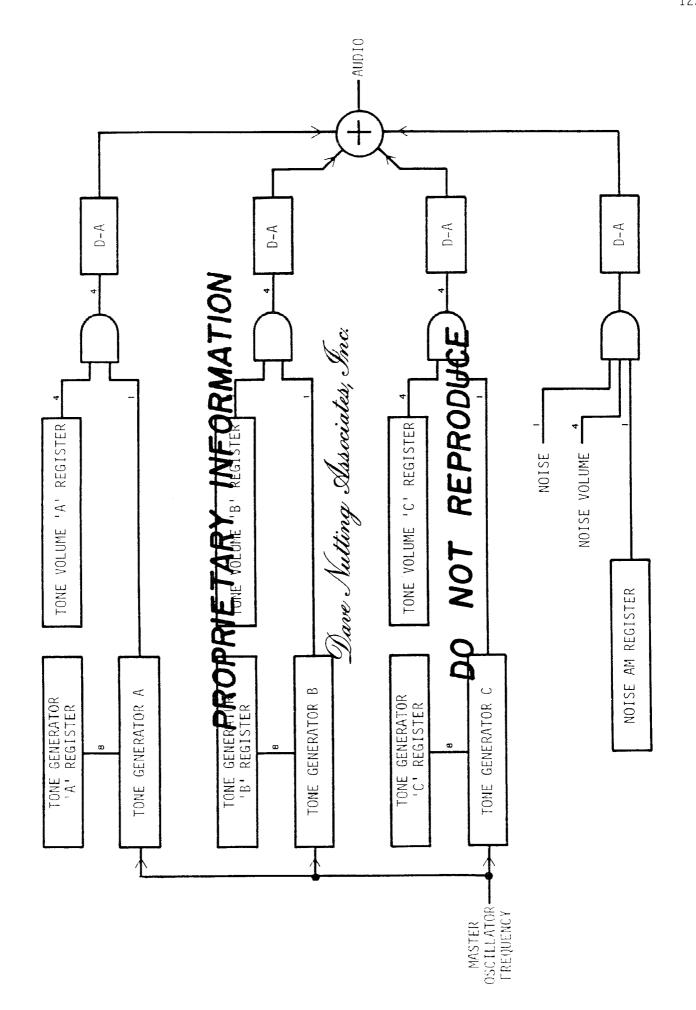

| 122 | Tone Generators                                |

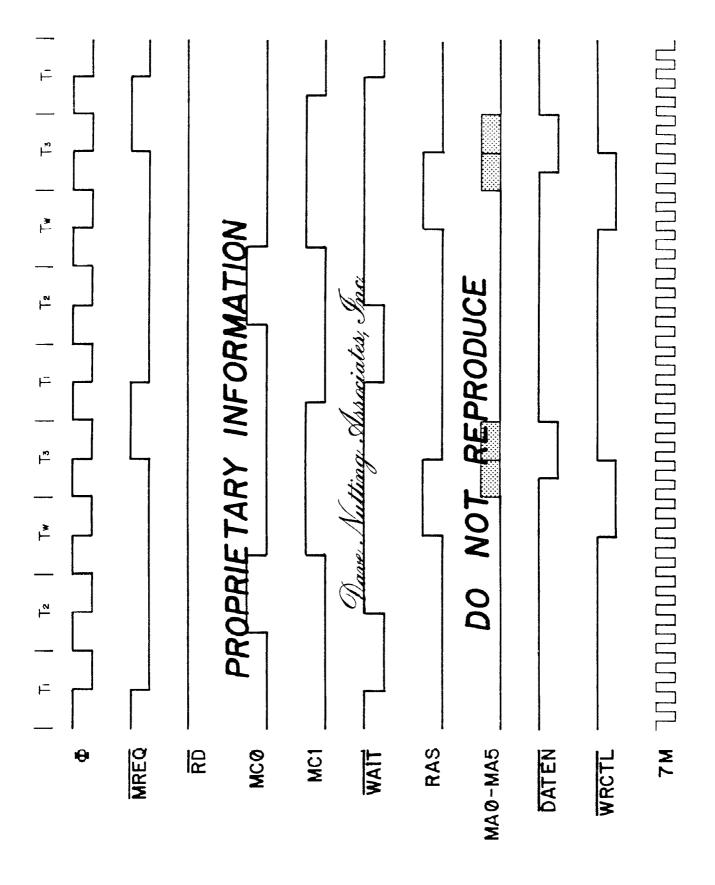

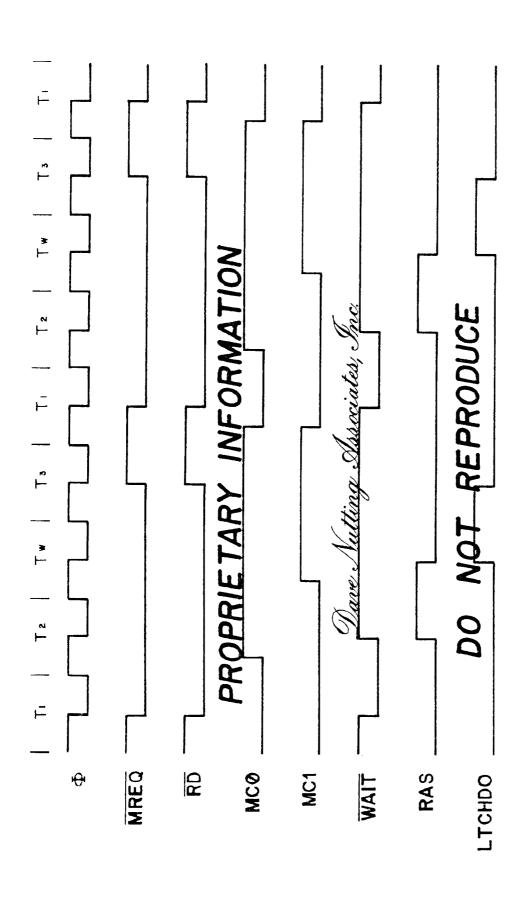

| 124 | Memory Write Without Extra Wait State          |

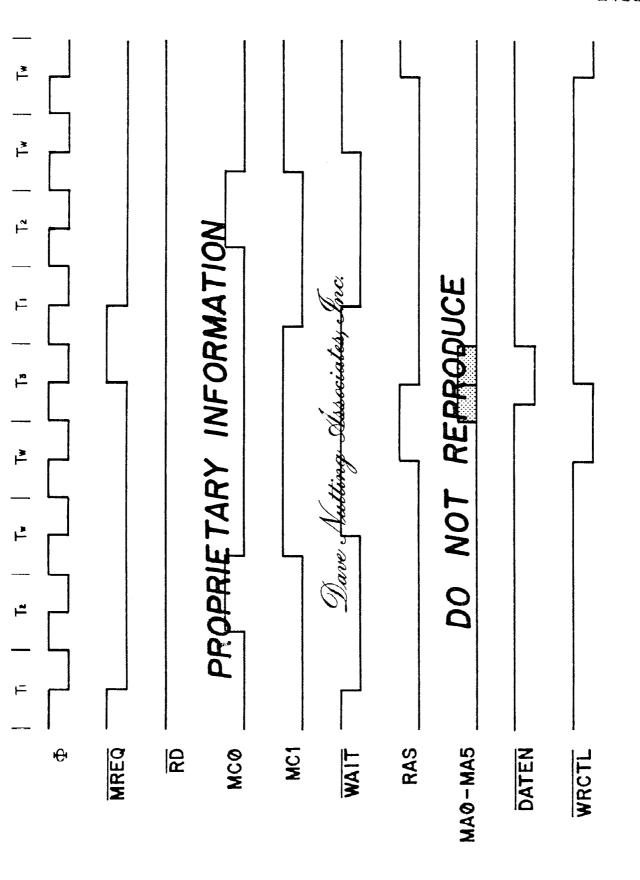

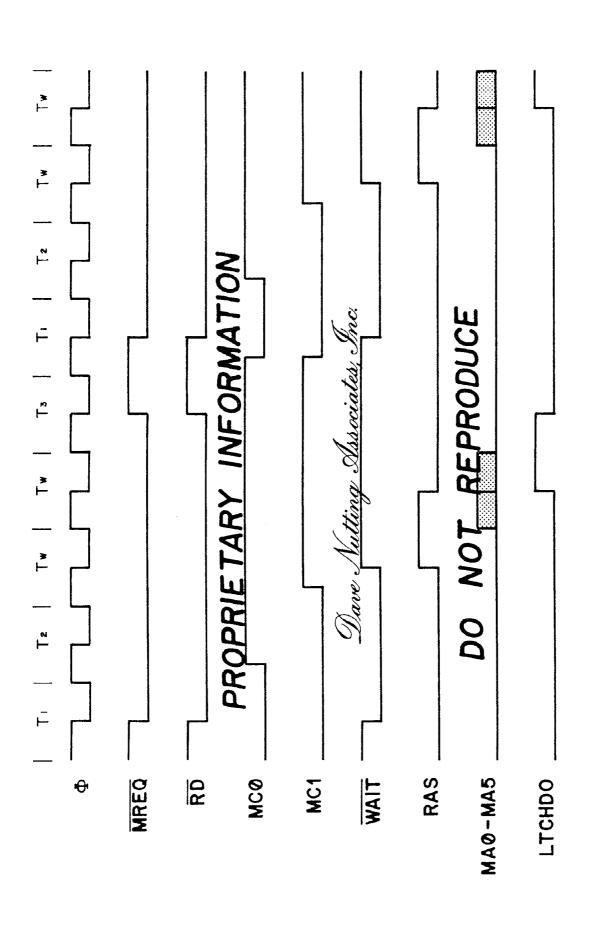

| 125 | Memory Write With Video Wait State             |

| 126 | Memory Read Without Extra Wait State           |

| 127 | Memory Read With Video Wait State              |

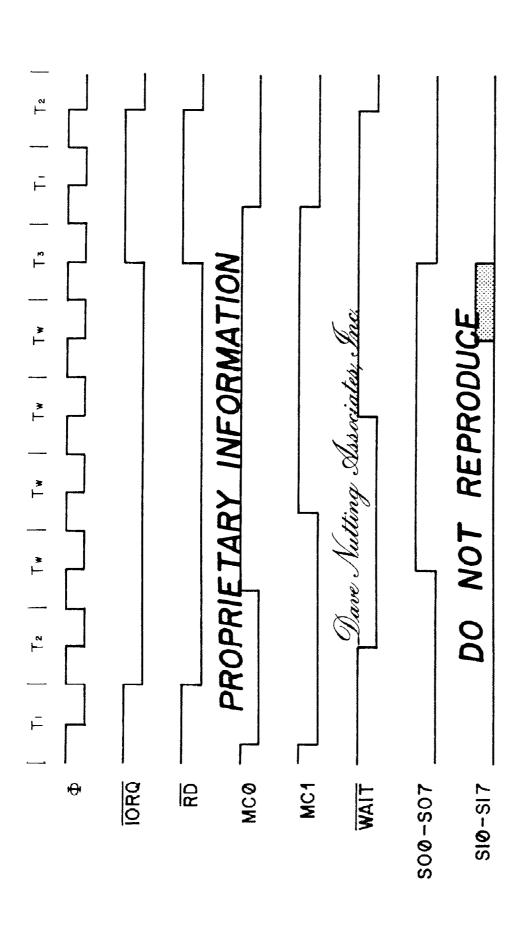

| 128 | I/O Read From Port 10H - 17H                   |

| 129 | I/O Read From Other Than Port 10H - 17H        |

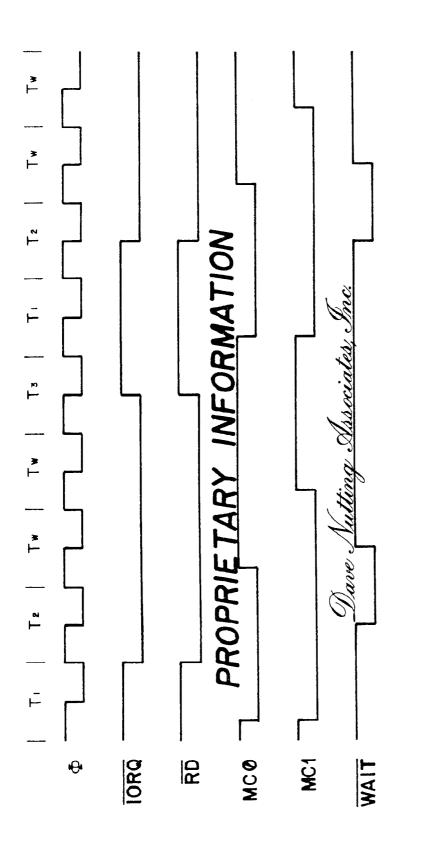

| 13Ø | I/O Write                                      |

| 132 | Relationship Between 7M, Horiz Dr, Vert Dr,    |

|     | $\overline{\Phi}G$ , $\overline{PX}$ , and RAS |

| 133 | Relationship Between Horiz Dr, Horiz Blank,    |

|     | Horiz Sync, and Color Burst                    |

| 134 | Relationship Between Vertical Sync,            |

|     | Vertical Blank, and Vertical Drive             |

|     |                                                |

• ..

#### HOME VIDEO GAME SYSTEM

This documentation describes the Bally Home Video Game System. The description begins with a discussion of the major sub-sections of the system. Following this, each sub-section is presented in greater detail, with detailed particulars, such as calling sequences and resource use.

The major sub-sections of the system are:

The User Program Interface...which allows cassettes to reference the system routines through a standard interface. Includes an interpreter.

The Screen Handler...a complex of routines for chating screen images. Includes facilities for initial vation, pattern, and character display, co-ordinate conversion, and object vectoring.

The Interrupt Processor...decrements timers, plan music, and produces sounds.

The Human Interface...reads keypad and control Endles, inputs game selection and options.

Math Routines...a package of routines for manipating floating BCD numbers.

#### USER PROGRAM INTERFACE

The User Program Interface (UPI) is a set of procedures and conventions, which are utilized by a cassette program to access the facilities provided by the home video game system. By adhering to these conventions a cassette program will be system independent, thus allowing improvements to be made to later versions of the system and board games, while maintaining upward compatability.

The basic rule for using the UPI

With exception to the system DOPE vector no cassette should extradress system ROM directly, or expect a given ce to always equat a certain value

The mechanism for calling a system routine is:

RST

DEFB (Partine # + opt@n)

where routine number is an even number specifying which sub-routine to transfer to, symbolic identifiers, which are equated to routine numbers, are provided in HVGLIB.

Option is used to specify how arguments are being passed to the system routine. In option equals zero, the arguments are presumed to exist in CPU registers; if option equals 1, the arguments are taken to follow in line after the routine number/option byte. These arguments are loaded into the CPU registers automatically before the called routine is entered. The arguments required by each system routine are given in the routine's detail documentation.

The SYSTEM macro generates the sequence previously mentioned with option =  $\emptyset$ :

SYSTEM (routine #)

(example)

SYSTEM FILL

The SYSSUK macro generates the sequence previous mentioned with option = 1:

SYSSUK (putine #)

Frequently it is desirable to string several system routine calls together. If four or more calls (follow in sequence, it is more efficient to utilize the interpreter. By using the interpreter we void the overhead of the RST 56 instruction by expecting a call index to immediately follow the call index or arguments used by the previous

Special call indexes are used to enter and exit interpretive mode:

#### Example:

system routine.

BEGIN INTERPRE SYSTEM FILL ROUTINE DO F SCREEN RTING AT TOP C DEFW CONTINUING FOR 92 LINES DEFW BYTEPL ;FILLED WITH ZE **DEFB** ;DO CHARACTER DELAY ROUTINE CHRDIS DO ;Y-AXIS POSITION F CHARACTER **DEFB** Ø ;X-AXIS POSITION OF CHARACTER **DEFB**  $1\emptyset$ ;OPTIONS-PLOP,10-ON,00-OFF DEFB :CHARACTER TO BE DISPLAYED DEFB 'A' ; EXIT INTERPRETER EXIT

ock of call indexes ha.

sette programs. If a negative or is macro routine address table and a containing of the address of th A block of call indexes have been set aside for the internal use of user's macro routine address table and argument table are utilized. The user is responsible for storing the addresses of these tables

#### SYSTEM ROUTINE CONVENTIONS

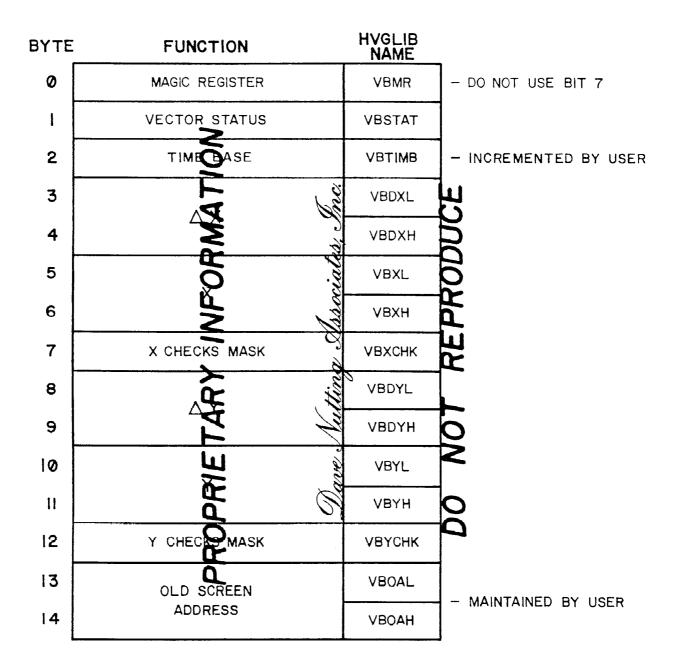

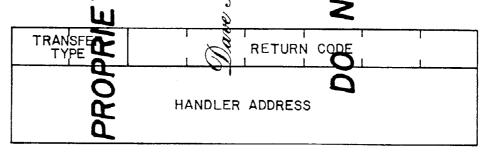

A system routine is coded like a conventional machine language subroutine, with the exception that output parameters are not passed through registers, but rather through the context block.

The context block is created by the RST 56 call. The user's register set (AF, BC, DE, HL, IX, IY) is pushed onto the cack. Register IY is set to point at this stack frame. Thus a copy of the input arguments exists in RAM which the system routine may refer to as needed. These arguments are also present in the registers when the system routine is entered hence it is only necessary to refer to the context block when one had lobbered an input argument.

An output argument is returned to the caller by setting it in the context block. It register was changed, but the associated cell in the context block was not, then the register will have it's old value on return. Thus a system routing is free to use any of the registers it needs without concern to saving and restoring. Moreover, the user can assume that re-registers will change except hose defined as returning an output argument.

The following illustration describes the context flock and equates provided in HVGLIB for each field.

Four tables are used by the UPI in the control transfer process. The first two tables gives the routines starting address indexed via call number. The systems table is named SYSDPT. The user may extend this table by storing the address of his extended table into USERTB, USERTB+1. This address should point 128 bytes before the first entry.

The other two tables describe what in line arguments a call that specifies in line arguments should expect. This table gives a one-byte bitstring, also indexed via call number. The systems name is MRARGT, the user's address is in UMARGT, UMARGT must point 64 bytes ahead. Arguments must follow the call in a specified order.

Note that the context contains additional information not shown. information exist Joth above and below the context. User programs should never use this information on even assume that it exists. The user should only address this are by using IY. DISPLACE EQUATE NAME MEMORY CELL BIYL X BIXH 3 4 CBE D CBD CBC 6 SBI 7 CBB П FLAGS BFLAG 8 CBA 9 A A CBL CBH

CONTEXT BLOCK FORMAT

Н

В

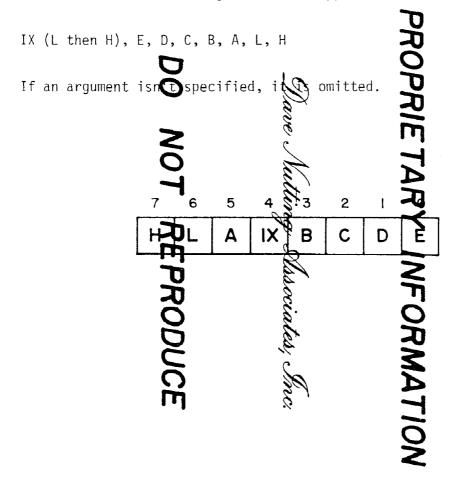

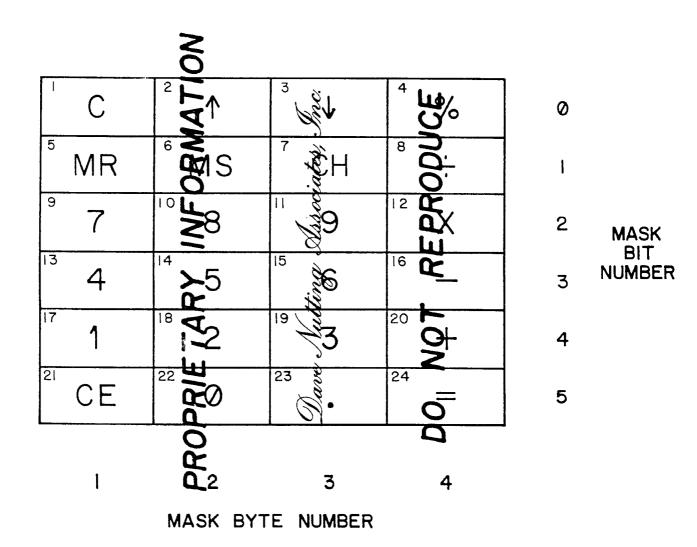

# IN LINE ARGUMENT MASK TABLE ENTRY TABLES MRARGT and UMARGT

If a bit corresponding to a register is set, the register is loaded. The order in which the arguments must appear is:

UPI INTPC

BEGIN INTERPRETING

Calling Sequence:

INTPC SYSTEM

Aruguments:

None

Notes:

Description:

See UPI description for explanation of interpredicts, Inc.

REPRODUCE

None

UPI XINTC EXIT INTERPRETER

Calling Sequence:

EXIT

Arguments:

None

Description:

This code causes the interpreter to exit. Execution of machine

instructions proceeds at the following location.

Restrictions:

This routine should only be called using the interpreter. A direct

system call would produce unpredictable (and catastrophic) results.

**PROPRIETARY**

UPI RCALL CALL ASSEMBLY LANGUAGE SUBROUTINE

Calling Sequence:

D0

or

RCALL

Arguments:

Description:

RCALL may be used interpreter. at the next instruction.

DONT

DEFW (routine

HL=address of routine

the subroutine returns, interretation proceeds

reives courol, HL will point

Sters will contained to the contained When the assembly language routing receives couldn't, HL will point at the routine's starting address the other relatives will contain their current vales. subroutine will not be passed along. To pass  $t_1$  output parameter, the subroutine must after the context block, which pointed at by IY.

Restrictions:

Assembler routine nust not dest

Example:

DEFB **RCALL**

DEFW **CLRAC**

CLRAC: XOR Α

RET

UPI MCALL

CALL INTERPRETER SUBROUTINE

Calling Sequence: SYSTEM MCALL or SYSSUK MCALL

DEFW (routine address)

HL=Subrougine Address

Description:

MCALL is used to Call an interpreser sequence as subroutine. MCALL

may be used from This language as well may be used from thine language as well as whin an interpreted sequence. Calls may be nested in initely, limed only by stack space (4 bytes per call) To exit the interpreted subrouting use MRET. PROPRIE TA Example: SYSSUK DEFW FILL+1 ;DO FILL NORMEM DEFW DEFW ØFFFH DEFB D0 MRET ;GO BACK TO CALLER

UPI MJUMP

INTERPRETER JUMP

Calling Sequence: DO MJUMP or DONT MJUMP DEFW (goto address) Arguments: HL=Go to Description: The current interpretive program counter is se o the contents of HL. The next instruct is fetched from that addre Restrictions: MJUMP must be cal from the inte The targets of all JUMPS preter. must also be interp eted sequençê PROPRIE Example: SYSTEM NTER INTPC STEP D0 MJUMP ; JUMP TO END OF DEFW END ; INTPC STEP END: DEFB XINTC ;EXIT INTERPRETER

UPI MRET RETURN FROM INTERPRETIVE SUBROUTINES

Calling Sequence:

DO

MRET

Arguments:

None

Description:

Description:

MRET causes execution to proceed at the instruction following the corresponding MCALMAN States and MCALL for March 1990.

Description:

MRET causes execution to proceed at the instruction following the corresponding MCALMAN States and MCALL for March 1990.

Description:

MRET causes execution to proceed at the instruction following the corresponding MCALMAN States and MCALMAN

#### SCREEN HANDLER

The screen handler is a group of routines for generating frame buffer images. Included are entries for filling sections of the screen with constant data, the animation of figures, and the display of alphanumerics.

Many of these routines utilize the MAGIC functions provided by the custom chips. Since the status of these chips dannot be context-switched, many of these routines are not re-entent. The user is responsible for preventing conflicts. This can be done by disabling interrupt, or imprementing a semannore.

PROPRIETARY IN

TON

SCREEN SETOUT SET DISPLAY PORTS

Calling Sequence:

SYSTEM **SETOUT**

or

SYSSUK SETOUT

DEFB BLINE\*2

DEFB HERIZX/4

DEFB

A=Data togoutput to IN (port EH)

B=Data to output to HO (port 9H) (port AH)

D=Data to output to VE

None

Outputs above data to orts

See hardware writeup for discussion of

above porss.

PROPRIETARY INFORMATION

Description:

Arguments:

Output:

SCREEN FILL

FILL A CONTIGUOUS AREA WITH CONSTANT

FORMATION

Calling Sequence: SYSTEM FILL

or

SYSSUK FILL

DEFW (first byte)

DEFW (number of bytes)

(deta to fill with) DEFB

A =Data to fill with

BC=number of bytes to f

DE=addres to begin fil

Description:

Arguments:

This routine sets the memory range DE to (DE+B11) to the

specified constant

Notes:

Fill can be used for screen clearing, or initialization of scratchpad

It is re-entrant. RAM.

SCREEN RECTAN

PAINT A RECTANGLE

Calling Sequence: SYSTEM RECTAN or TARY INFORMATION SYSSUK RECTAN DEFB (X co-ordinate) DEFB (X co-ordinate) DEFB (M) size) (Wsize) DEFB DEFB (💸lor mask) A =Color mask to write retangle with Arguments: B =Y-size of rectangle m pixels C =X-size of rectangle in pixels D = Y co-ordinate for Ullforner of rectangle E =X co-organate for UL corner of rectangle Description: A rectangle of specified size of color mask is matten at X,Y. uses the MAGIC furtions and is not re-entrant. Put up a 3 X 4 rectangl of color 2 at 15,13. Example: RECTAN DO DEFB 15 **DEFB** 13 DEFB 3 DEFB DEFB 1Ø1Ø1Ø1ØB

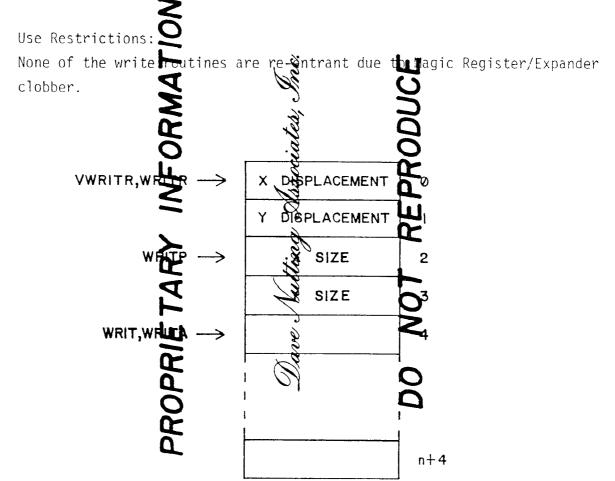

#### SCREEN WRITE ROUTINES

Virtually every video game involves the manipulation of animated figures. These figures are composed of patterns which are arbitrary pixel arrays. The write routines are used to transfer such patterns to the screen.

Five hierarchical levels of call are supported. The levels differ in the amount of preprocessing required by the user before calling. The highest level assumes that most of the parameter reside in a standard data structure, while the lowest evel presumes that all arguments are in registers with all attendant transformations such as relative-to-absolute conversion) already accordingle. The tive levels are:

- (1) Write from a Vector

- (2) Write Relative

- (3) Write Variable Pattern

- (4) Write (5) Write Absolute

Two transformations of the pattern may be performed prior to writing. They are FLOP and EXPAND. FLOP mirroring the pattern on the X-axis. EXPAND is the translation of a 1-bit per pixel pattern into a 2-bit per pixel pattern. Since many patterns are only two-color, this allows for more efficient pattern storage. SLOP and EXPAND can both be done at the same time.

Three writing mode may be used. They are PLOP, OR, and XOR. PLOP is a conventional store into RAM. If OR is optioned, the data being written is ORed bit by bit with whatever was already there. Similarly, if XOR is set, the pattern is XORed with that beneath. Use of OR or XOR takes slightly longer since a read before write must be performed.

Note that ROTATE is not currently supported in software due to space considerations.

### STANDARD CALLING SEQUENCE

Every write routine uses a subset of the following argument/register assignment:

A = Magic Register

BOLLY Pattern Size in Bytes

CO X Pattern Size in Bytes

DY X Co-ordinates (Ø - 101)

Pattern Address

Vector Address

Vector Address

#### PATTERN REPRESENTATION

The higher the level of the write routine, the more ancillary information is stored with the pattern. The following diagram shows what each level expects. Any bytes of lower address than the pointer for a given level, need not be specified.

SCREEN WRITE VWRITR WRITE RELATIVE FROM VECTOR

Calling Sequence:

SYSTEM VWRITR

or

SYSSUK VWRITR FORMATION

DEFW (vector)

DEFW (pattern)

HL=Patter& address

IX=Vector Address

DE=Absolu address us

A =Magic egister used

Description:

Arguments:

Output:

The co-ordinates and magic register are loaded from the specified (See vector routine document) The relegive co-ordinates stored with the pritern are added to the co-ordinates from the vector. The pattern size is also taken from the pattern and writing proceeds.

Notes:

If expansion is to be done, the OFF color must be set by the user before calling VWOTR.

SCREEN WRITE WRITR WRITE RELATIVE

Calling Sequence:

SYSTEM WRITR

or

SYSSUK WRITR

DEFB (X co-ordinate)

DEFB (Y co-ordinate)

DEFB (Magic Register)

Rattern addre DEFW

HL=Patters address A =Magic egister

D = Y co-odinate

E = X co-ordinate

DE=Scree Address Used

A = Magic Register Use

Description:

Arguments:

Output:

ARY INFORMATION The relative co-dedinates stored with the pattern are added to the co-ordinates passed in DE. Pattern size is taken from the pattern.

Notes:

If expansion is to be done, the ON/OFF color men be set by the user before calling WRITR.

SCREEN WRITE WRITP WRITE WITH PATTERN SIZE SCARE UP

Calling Sequence:

SYSTEM WRITP

or

WRITP SYSSUK

(X co-ordinate) (Y co-ordinate)

(Magic Registe

attern addre

A =Magic Register Used

SYSSUK WRITP

DEFB (X co-ordinate)

DEFB (Y co-ordinate)

DEFW Rattern add

Arguments:

HL=Pattern Address

A = Magic Register

D = Y co-ordinate

E = X co-ordinate

DE=Screen Address Us

A = Magic Register Us

Description:

The pattern size at taken from the pattern.

Notes:

Notes:

User must worry a put ON/OFF if expansion

SCREEN WRITE WRIT WRITE PATTERN

Calling Sequence:

WRIT SYSTEM

or

SYSSUK WRIT

(X) pattern size

A =Magic Register to use

SYSSUK WRIT

DEFB (X co-ordinate)

DEFB (Y co-ordinate)

DEFB (X pattern size)

DEFB (X pat

SCREEN WRITE WRITA WRITE ABSOLUTE

Calling Sequence:

SYSTEM WRITA

or

DE=Absolute screen address of upper lefthand comper of where to write

DEFM

Ments:

HL=Pattern Adv

A = Magic legiste

B = Y Pattern size

C = X Pation size

DE=Absolute screen addresser of where to hand conser of where to hand conser of where to hand conservations are not output to (MAGIC); it is not odecide whether and hand conservations are not output to (MAGIC); it is not odecide whether are not output to (MAGIC); it is not odecide whether are not output to (MAGIC); it is not odecide whether are not observed. magic memory.

SCREEN SAVE SAVE AREA

Calling Sequence:

SYSTEM SAVE

or

SYSSUK SAVE

DEFW (save area)

DEFB (X size)

DEFB (Yisize)

DEFW reen addres

INFORMATION B =Y size sf area to sa

C =X size of area to say (in bytes)

DE=Addressof save area

address of oper left-hand corner

Description:

Arguments:

SAVE is used to preserve what is 'waderneath' a moving pattern. SAVE copies the indicated area of the  $\aleph$  reen to the save area. The sizes of the area which was aved is preserved in the first two bytes of the save area.

ust be greater than or equal to the X-size times the The save area size Y-size plus 2.

The save area may MAGIC or non-MAGIC. SCREEN RESTORE RESTORE AREA

Calling Sequence:

SYSTEM RESTOR

or

SYSSUK RESTOR

(Save area)

(Screen address)

DE=Save area to restore from

HL=Absolice address of upper left-hand corner

of area to restore

DEFW

DEFW

DEFW

DE=Save

HL=Abso

of an

Description:

RESTORE is the interse of SAVE. The size of tlearea to restore is

taken from the fix two bytes of 🕃 he save area

**PROPRIE TARY**

SCREEN VBLANK

BLANK FROM VECTOR

Calling Sequence:

SYSTEM VBLANK

or

SYSSUK VBLANK

DEFW (Vector address)

DEFB (X size)

DEFB (Size)

D = Y si

E =X size (in bytes)

IX=Vector address

Arguments:

Description:

The BLANK bit in the vector status byte is tested. If it is not set, no blanking is done. If it is set, it is resent then the old screen address is taken from the vector and blanking is done. If FLOPPED is specified by the Magic Register byte in the vector, a flopped blank is done. VBLANK always blanks to zero.

PROPRIET

FORMATION

00

SCREEN BLANK BLANK AREA

Calling Sequence:

SYSTEM BLANK

or

SYSSUK BLANK

DEFB

(X size)

DEFB

(Y size)

DEFB

(B) ank to)

DEFW

INFORMATION

ank address

HL=Blank address (not M

B =Data toblank to

Arguments:

SCREEN SCROLL SCROLL WINDOW

Calling Sequence:

SYSTEM SCROLL

or

SYSSUK SCROLL INFORMATION DEFW (line increment)

DEFB (# of bytes)

(a of lines) **DEFB**

(jirst byte) DEFW

B = Number of lines to Arguments:

> C = Number of bytes on to scroll

DE=Line iacrement

HL=First Byte to scrol

Description:

This routine copie NBYTES from Frst line +INC to first line.

Thus to scroll up and, HL points at the first ine (which is overwritten) and the line increment would be positive. To scroll downward HL points at the lit line and the line increment would be negative.

The value in HL is an absolute address calculated by:

BASE OF SCREEN + #BYTES IN X OF SET +(#lines of Set\*byte per line)

Note:

This routine can  $\mathbf{S}_{\mathbf{H}}$  be used to scroll one line at a time.

SCREEN ALPHANUMERIC

ALPHANUMERIC DISPLAY ROUTINES

HVGSYS provides several routines for the display of alphanumeric information. This section provides information which is common to all of the alphanumeric display routines.

The ASCII character code is used to represent all strings, with the following extensions:

Character with hex equivalents in the ringe 1 - 1F are interpreted as tabulation codes which cause the character display routines to skip over N character positions before writing the following characters.

The characters 20H to 63H are displayed as 5 X 7 standard graphics with 3 pixels of norizontal spacing and 1 pixel of vertical spacing.

The characters between 64H and 7FH are atterpreted by STRDIS as control codes which cause the contents of registers C, DE, and IX to be changed to the value that follow the string.

See table a companying STRDIS.

The charagers between 8ØH and FFH are taken as references to a user supplied alternate character font.

The following argument/register combinations are used by all of the alphanumeric display routines.

Register C contains the options byte formatted as shown below.

ENLARGE FACTOR specifies if the character is to be enlarged in size. The table below defines the possible values for this parameter. 😝 writes are performed through magic memory. Use XOR/OR WRITE of one of these of character to ORed/XORed with what was beneath ¶ ON/OFF COLOR characters are stored one per pixel, but are written two bits prixel by use of the expander. This field specifies the pixel values translate the ne bit per pixel representation into. For example, the value 1101 specifies that the threground color is 11, and the background color is Ø1. OPTION B ENLARGE OR S WRIJE ON COĻOR **XOR** OFF FACTOR 1 WRITE COLOR **ENLARGE** HOW MANY ENLARGED SIZE FACTOR TIMES LARGER OF SINGLE PIXEL ØØ 1 1 X 1 Ø1 2 2 X 2  $1\emptyset$ 4 X 4

8 X 8

8

11

D register contains the Y co-ordinate and the E register contains the X co-ordinate. These co-ordinates give the address of the upper left-hand corner where the first character will appear. Upon return, these registers are updated to give the address of the character to the right, (or below if no more space exists on the line). This simplifies the composition of complex messages.

IX register contains the Alternate Font Descriptor. It is required only if alternate ront is referenced in call. Each character must be stored in one-bit per pixel format.

The small (3 X 5) tharacter set is displayed using this facility. A word in the system DOPE vector points at a standard alternate font descriptor for this character set?

The format of the alternate font descriptor is frown below. equal to first character in table character size in bits + x spacing BASILICHARACTER  $IX \rightarrow$ X FUME SIZE 1 CHARACTER SON IN BITS + Y SPACING E SIZE 2 X PATERN SIZE 3 EACH CHARACTER TABLE ENTRY SHOULD BE OF SIZE X PATTERN\*Y PATTERN SIZE 4 Y PATTERN SIZE 5 CHARACTER TABLE ADDRESS 6

SCREEN ALPHANUMERIC DISNUM DISPLAY BCD NUMBER

Calling Sequence: SYSTEM DISNUM

or

SYSSUK DISNUM **DEFB** (X)

(Y)DEFB

(ditions) **DEFB**

DEFB tended opti

DEFW (mmber addres

Arguments: B =Extended options

C = Standar alphanumeric ptions byte

DE=Standar X,Y co-ordinate

HL=AddresSof BCD number

TARY INFORMATION IX=Optional character flut descriptor \*NOT LOADED

Outputs: DE=Updatec

Decription:

This routine displays the standard BCD codes  $\emptyset$  through 9. In addition,

the codes AH through FH are also defined. The interpretation for

these codes are:

If leading zero suppress is set, then instead of displaying a leading zero, a space is displayed. The first non-zero nibble encountered terminates leading zero suppression (including A - F). If the number is zero, a single zero is displayed.

If alternate font is set, the routine will display using codes between AAH and B9H (zero starting at  $B\emptyset H$ ).

SCREEN ALPHANUMERIC DISTIM DISPLAY TIME

Calling Sequence:

SYSTEM DISTIM

or

SYSSUK DISTIM

DEFB

(X co-ordinate)

DEFB

INFORMATION

(Y co-ordinate)

DEFB

(Sptions)

M

Arguments:

DE=X,Y coordinates

X =Option (see note

IX=Alternate Font Descriptor

Outputs:

DE=Update

tor (not loaded)

Description:

This routine displays the system time (GTMINS, O O O at the coordinates specified in the form MS:SS, where M=minutes, S=seconds.

Seconds are optional.

101

Notes:

The small character set is used and one level of enlarge factor is permitted.

Options are the sum as the alphanumeric display routine except that bit 7=1 to display colon and seconds; bit 7=0 to suppress colon and seconds.

SCREEN ALPHANUMERIC CHRDIS DISPLAY CHARACTER

Calling Sequence:

SYSTEM CHRDIS

or

SYSSUK CHRDIS

DEFB (X co-ordinate)

**DEFB** (Y co-ordinate)

(ogtions) **DEFB**

DEFB (Character)

INFORMATION Arguments: A =ASCII caracter to d

C = Standar options byt

DE=Standary Y,X co-ordinates to begin at

IX=Optional alternate for descriptor address

DE=Update to next frame

Description:

\*NOT LOADED

Outputs:

This is the basic ch f tabulation is arcter display3promative. specified, the co-ordinates are updated but no Qual writing occurs.

Notes:

Observe that IX is not loaded by the UPI SUCK fallity. If alternate font is used, IX must be loaded with alternate out descriptor address.

Since this routine uses magic memory, it is not re-entrant.

SCREEN ALPHANUMERIC

STRDIS

DISPLAY STRING

Calling Sequences:

SYSTEM STRDIS

or

SYSSUK STRDIS

DEFB (X co-ordinate)

DEFB (Y co-ordinate)

DEFB (O**p**tions)

DEFW **C**ring)

INFORMATION Arguments: HL=String &ddress

C =Standar Options

DE=Standar& Co-ordinate tor Address IX=Alternade Font Descr

Outputs: DE=Update to next frame

Description:

\*NOT LOADED

The string pointed by HL is displayed as opt The string is

terminated by a zero

Notes:

Notes:

IX is not loaded SUCK.

### STRDIS INTERPRETATION OF CODES 64H to 7FH

STRDIS responds to the charcter codes between 64H and 7FH. These codes are taken to specify that certain registers in the context block are to be set to new values. This facility is useful for changing size, write mode, screen co-ordinates, or fonts, during a single STRDIS call.

The following table specifies which registers are loaded for a given code. The order in which the new register data follows the code, is also represented.

|     | ~                  | , je           | 7             |

|-----|--------------------|----------------|---------------|

| 64H | c <b>S</b>         | 72             | IX,D 6        |

| 65H | E                  | 73             | IX,E,D        |

| 66H | D, G               | Z Đ            | IX,C          |

| 67H | E <del>,B,</del> C | <b>A</b>       | IX,E,C        |

| 68H | NONE               | 764            | IX,D,C        |

| 69H | ₽<br>F             | 7.2            | IX,E,D,C      |

| 6AH | DA                 | √ <b>23</b> 4  | IX            |

| 6BH | E D                | 797            | IX,E          |

| 6CH | CLU                | 7 A <b>y</b> i | IX,D <b>Z</b> |

| 6DH | E                  | 7 B            | IX,E,D        |

| 6EH | D                  | <b>3</b>       | IX,C O        |

| 6FH | E 📭                | 7DH            | IX,E,C        |

| 7ØH | I                  | 7EH            | IX,D,C        |

| 71H | I Q                | 7FH            | IX,E,D,C      |

|     |                    |                |               |

### SCREEN VECTORING - VECTORING ROUTINES

Most games involve moving patterns. Most moving patterns move along a line. The home video game operating system provides the vectoring routines to facilitate programming such pattern motion.

The vectoring routines work with a memory array called a vector.

Represented within this vector are the co-ordinates of an object, the velocities of the object, and the negessary status information to control the object. Ty periodical invoking the vectoring routine, this data is updated and to be used to direct the motion of a pattern.

More formally, a vectored object possesses an X and Y co-ordinate. Associated with these co-ordinates are velocities X and  $\Delta Y$ , which are added to X and Y every time increment. Dince the screen is finite, there also exists two upper and two lower limits  $X_{LU}$ ,  $X_{LL}$ ,  $Y_{LU}$ , and  $Y_{LL}$ , the attainment of which requires solutresponse.

The HVGSYS vectoring poutine allows for two different responses to a limit attained. Exper the sign of the delta is reversed or vectoring is stopped for this to ordinate. This is specified by a flag byte. When attainment occur, this fact is pindicated by a status byte. Also the co-ordinate is several to the limit that was attained, preventing over-shoot.

Utilization of the varioring routines involves a number of user responsibilities. The user must properly initialize certain fields in the vector array. He must increment the time base byte, and periodically call the vectoring routine. Status bits must be checked and writing must be done.

To insure high-accuracy, co-ordinates and deltas are double-precision. The assumed binary "decimal point" is between the high and low order byte.

The following diagrams explain the layout of the vector array and the attendant user responsibilities.

## VECTOR BLOCK

## VECTOR STATUS DETAIL ACTIVE BLANK NOT USED VBSACT ACTIVE by user to indicate that vector is active. The coring routines will do no bucessing if reset. be initialized by user to eset state. Thereafter BLANK **W**IT and VBLANK bit is maintained by the em routines. CHECKS MASK DETAIL REVERSE DELTA SIGN NOT LIMIT LIMIT NUSED USEL VBCLAT VBCREV VBCLMT Sat by user to indicate that the co-ordinate is LIMIT CHECK oe limit check**e**d. et by user to indicate that we this co-ordinate REVERSE DELTA attains it's limit, the sign of the associated delta Cto be reversed. This can be used to cause objects √bounce' off barriers. Set by system if the limit was attained this call. LIMIT ATTAINED Otherwise it is reset. If the delta was not changed,

either by Reverse Delta or user, this bit will stay set.

SCREEN VECTORING **VECT** VECTOR OBJECT IN TWO DIMENSIONS

Calling Sequence:

SYSTEM VECT

or

SYSSUK VECT

SYSSUK VECT

DEFW (Vector address)

DEFW (Limit table)

HL=Limit table address

IX=Vector address

IX=Vector address

Output:

C = Time base used

Z = True, is it did not reve

Description:

If the vector is fractive, control is returned impediately. Otherwise VECTC is called for X, then Y. The zero status  $\Omega$  determined by comparing the new co-ordinate value with it's old value. If the high-order byte charged, then the bject moved. Zero status set if object did not mote, reset if object moved.

PROPRIE

SCREEN VECTORING VECTO VECTOR A CO-ORDINATE

ORMATION

Calling Sequence:

SYSTEM VECTC

or

SYSSUK VECTC

DEFW (co-ordinate address)

DEFW (Limit table)

Arguments:

IX=Pointer to low-order the of delta for co-ordinate HL=Limits to low-order this ordinate (if required)

C =Time bas♠to use

Description:

This routine operates on the subset of the vector array associated with a single co-ordinate. This subset consists of the delta co-ordinate and checks mask. This entry is provided so special vectoring schemes may be implemented such as 1 dimensional or 3 dimensional vectoring.

This entry adds the delta to the co-ordinate time base times. It ther performs the limit dhecks for the co-ordinate imperioned.

Note that this engy <u>does not</u> interrogate or alter any bytes in the vector array outs to of the defined subset. Here the active bit isn't checked.

SCREEN RELABS CONVERT RELATIVE CO-ORDINATES TO ABSOLUTE MAGIC ADDRESS AND SET UP MAGIC REGISTER

Calling Sequence: SYSTEM RELABS or

NFORMATION SYSSUK RELABS

DEFB (Magic register value)

A =Magic Register valuato set

D = Y co-ondinate

E = X co-odinate

A =Magic Register value, with proper shift amount set DE=Absolue memory add (MAGIC)

Description:

Output:

Arguments:

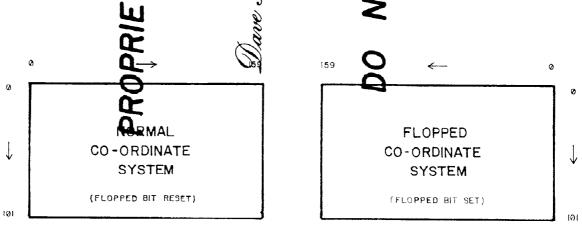

The low-order two bits of the X co-ordinate arounserted into the magic The appointe memory address corresponding to register value bostring. the co-ordinate computed, taking into consideration the value of the The co-ordinate systems used are sown below. flopped bit.

SCREEN RELAB1

CONVERT RELATIVE ADDRESS TO ABSOLUTE NORMAL ADDRESS

Calling Sequence:

SYSTEM RELAB1

or

SYSSUK RELAB1

A =Magic register value to combine with shift amount

SYSSUK RELAB1

DEFB (Magic register value)

A = Magic register value to combine with shift D = Y co-ordinate

E = X co-ordinate

Output:

A = Combiner magic registry value

DE=Absolution normal address (not magic)

Description:

This routine is identical to RELABS except that I non-magic address is returned and the hardware magic register is fift set. The flopped is returned and the hardware magio register is at set. The flopped bit is interrogated and the flopped co-ordinate system is used,

if optioned.

**PROPRIETA**

COLSET SCREEN SET COLOR REGISTERS

Calling Sequence:

SYSTEM COLSET

or

SYSSUK COLSET

(Address of color list)

HL=Color list laid out

COL3L=first

COLOR last 🤏: COLOR woul**y**e at a higher

address than COL3L

Description:

Inputs:

This routine sets flor registers and saves add use by PIZBRK and PLAKOUT for color restoration and saves addass of colors for

PROPRIE TARY

HUMAN INCSCR INCREMENT SCORE AND COMPARE TO END SCORE

Calling Sequence:

SYSTEM INCSCR

or

INCSCR SYSSUK

Score incremented and det onally game over bit set

DEFW (address of score)

Arguments: HL=Address of score (must be 3 bytes long)

Output: Score incremented and dot onally game over bit

Description:

The 3 byte score printed at by HL BCD with low order byte at lowest address) is incremented (by 1) and compared to the end score (ENDSCR). If the end score (GSBSCR) was set in the game status byte (GAMSTB) and end score has been reached, then the game over bit (GSBEND) is set

in the game status byte.

PROPRIE TARY

HUMAN PAWS

PAUSE

Calling Sequence:

SYSTEM PAWS

or

SYSSUK PAWS

DEFB (number of interrupts)

Arguments:

B=Number of interrupts to wait

Description:

This routine provides for a pause for certain beer of interrupts. If used with ACT  $\mathfrak{P}_1$ , 60 will be  $\mathfrak{F}_2$  1-second parts This routine does an EI upon enery and assumes interrupts w

**PROPRIE TARY**

HUMAN KEYBOARD KCTASC KEY CODE TO ASCII

Calling Sequence:

SYSTEM KCTASC

Arguments:

B=Key code (not loaded)

Output:

$A \hbox{\it =} ASCII \ equivalent of keycode}$

Description: This routine does a table look-up

| KEYCODE NIME GRAPHIC HEX V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | /ALUE |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| 1 Cor Co                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |       |

| Common Co |       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |       |

| 8 Divide                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |       |

| 11 9 9 9 9 9 9 9 1 1 2 1 3 9 1 2 A 1 3 1 3 1 3 1 3 1 3 1 3 1 3 1 3 1 3 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |       |

| 14 5 5 36 15 16 Minus - 20 21                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |       |

| 17<br>18<br>19<br>20<br>20<br>PID<br>17<br>20<br>21<br>21<br>21<br>21<br>21<br>21<br>21<br>21<br>21<br>21<br>21<br>21<br>21                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |       |

| 20 P1 + 2B<br>21 C1 Entry CE 26<br>22 Ø Ø 30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |       |

| 22 Ø 3Ø<br>23 Decimal point . 2E<br>24 Equals = 3D                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |       |

HUMAN CONTROLS & KEYPAD SENTRY SENSE TRANSITION

Calling Sequence:

SYSTEM SENTRY

or

SYSSUK SENTRY

DEFW (Key mask address)

DE=Keypad mask table

Description:

Arguments:

SENTRY checks for changes in the potentiometer (pots), control handles, triggers keypad, semipheres and counter/timers. It also takes care of blackout. Blackouts is the automatic blacking-out of the screen after 455 seconds without a change. If SENTRY isn't called then the game will not black out

SENTRY checks if IMOUT equals on entry and if zero, it goes to PIZBRK. If a key has gone down a control handle changed, then TIMOUT is set to FFH.

HL should point and keypad mask. The keypad consists of 6 rows by 4 columns.

Example mask of  $\bigcirc$  DEFB Ø111ØØB just Ø - 9 DEFB 1111ØØB DEFB Ø111ØØB DEFB ØØØØØØØ

See diagram on following page.

Output:

A=Return code

B=Extended code

| PRIORITY | <u>A=</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | MEANING                                                  |

|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|

| 1        | SNUL<br>SEE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Nothing changed  Counter/timer Ø decremented to Ø        |

|          | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                          |

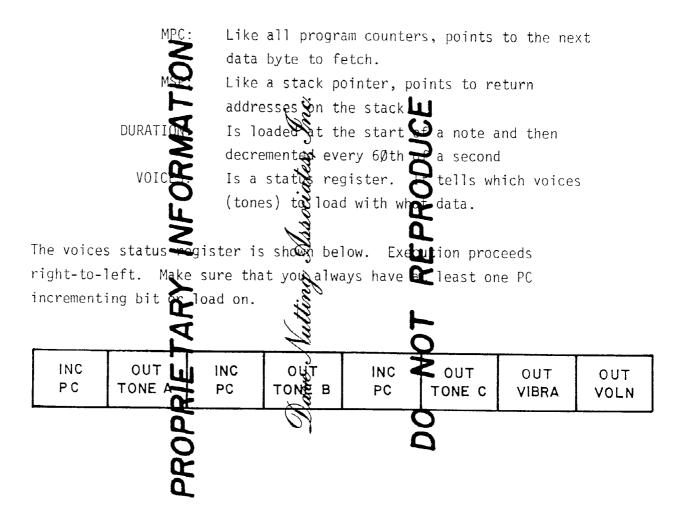

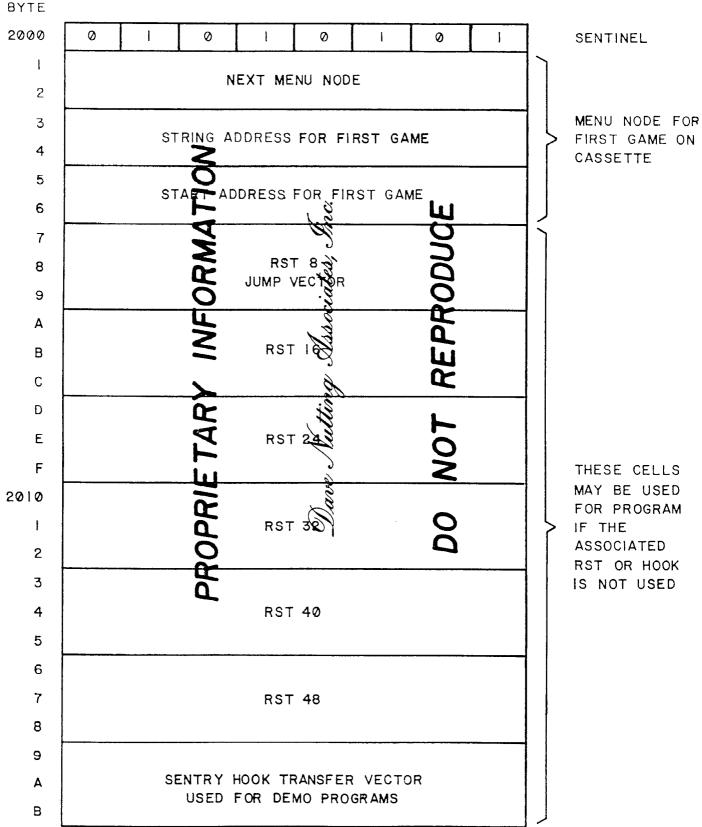

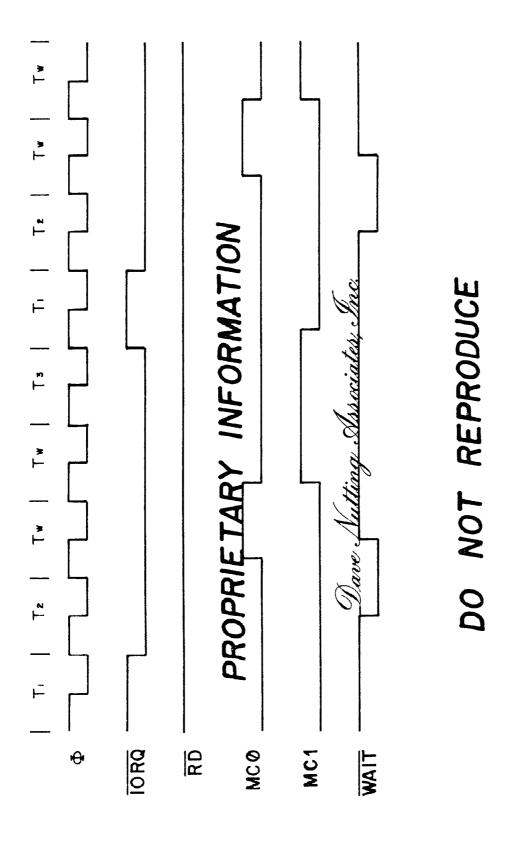

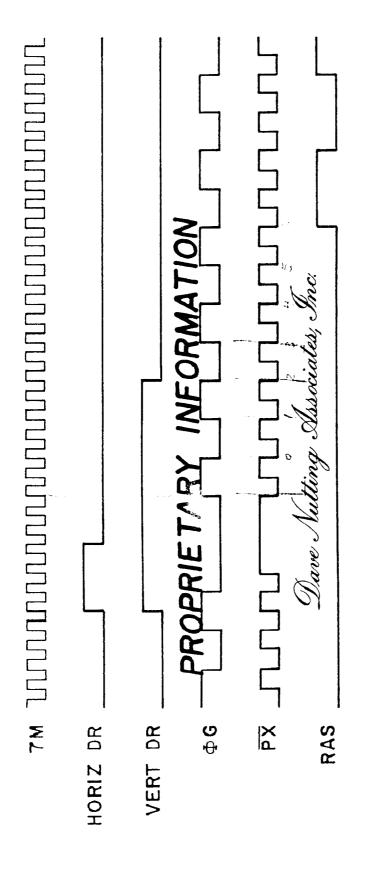

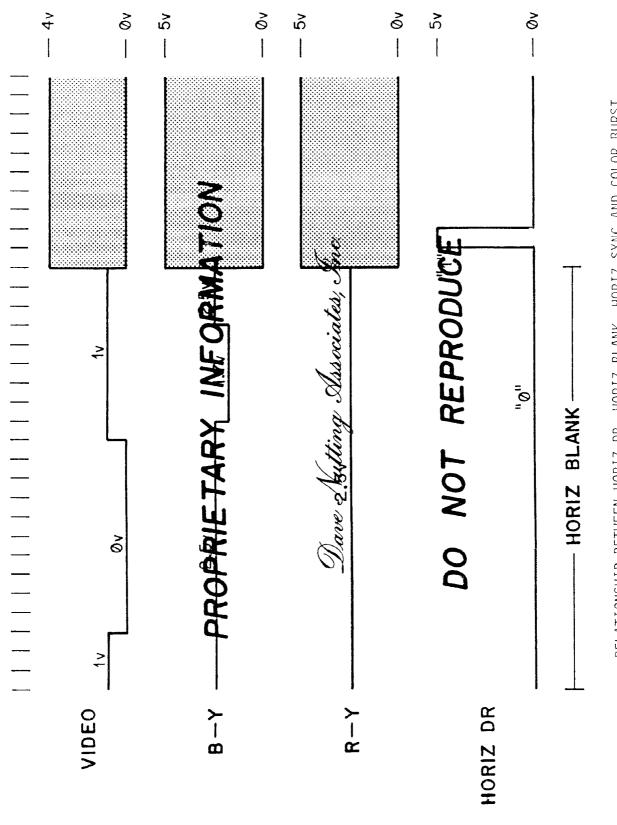

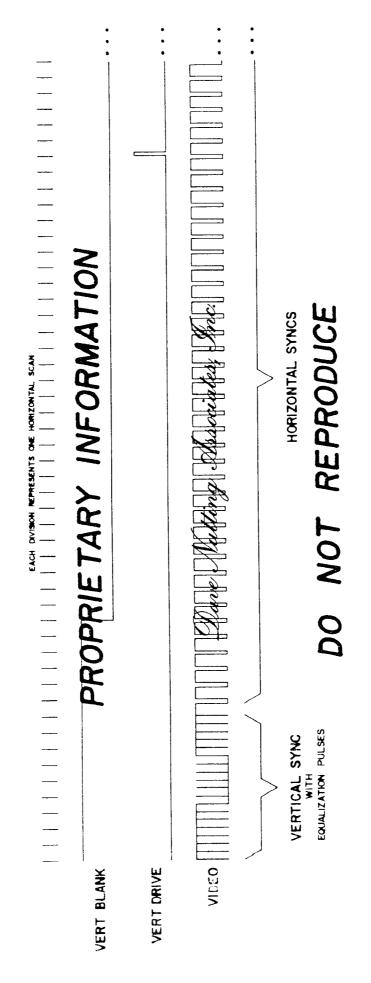

| 1<br>2   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Counter/timer Lecremented to Ø                           |